## Silicon Photonics Integration: A story of money and power

Peter Wilson, Ke Li, Dave Thomson, Fred Gardes

## We live in a communications world

- Internet

- Networks

- Wireless

- Sensors

- Global

- Social Media

- Instant

# What is the vision for an integrated Silicon Photonics World?

#### Low Cost

Simple Integration with CMOS

Low Power

**Standard Platforms**

and Computer Science

## But, there's a problem....

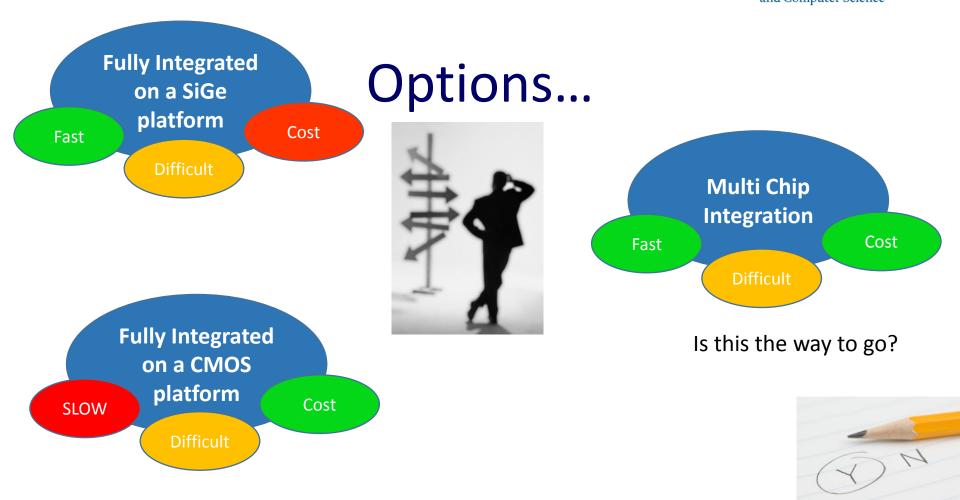

## An incompatible technology division?

Photonics Fast High Power Novel Materials Electronics Low Power Mobile Cheap

## How can we address this challenge?

What options do we have? What has been done? What resources do we have?

## How do we quantify the choices?

**Engineering and Physical Sciences**

**Research** Council

Speed of Operation (Gb/s) Power consumption (W)

But what about the cost?

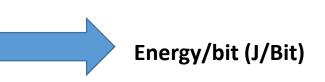

## We need to consider the costs...

As a research team, given by the limited research resource, what is the fabrication cost *per bit*?

Dollars/bit (\$/bit)

## **Example IC Fabrication Costs...**

IBM 180nm SiGe (40) IBM 130nm SiGe (40) IBM 130nm CMOS (40)

...and TSMC 65nm is \$21000 for 100 samples

# Choice for electronics devices depends on budget....

Unlimited budget and no power issues => SiGe "No" budget and limited power => CMOS

But we need to think about more than just a single demonstrator.....

## Additional benefit of CMOS?

- Reduced costs open the possibility of multiple runs and a research platform for different modulation formats.

- SiGe/GaAs **CMOS** Operation Operation speed speed **Multiple runs** Different modulation formats DSP Fabrication Power Fabrication Power

consumption

consumption

cost

cost

### **Strategy for practical success...**

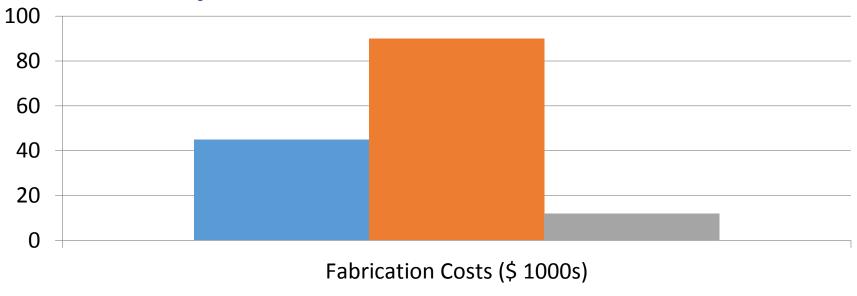

- Use CMOS for electronics

- Low cost, low power

- Custom Silicon for Photonics

- High performance, made in Southampton

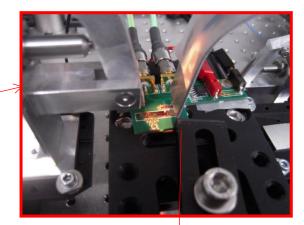

- Hybrid Integration using bonding

- Optimal platforms, rapid prototyping of separate technologies, simple integration

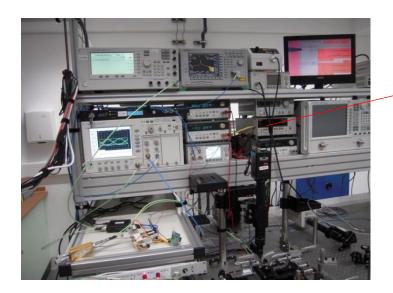

#### 1<sup>st</sup> Gen driver integrated with modulator based on 0.35um CMOS

1Gbit/s

#### **Achievement in 2012**

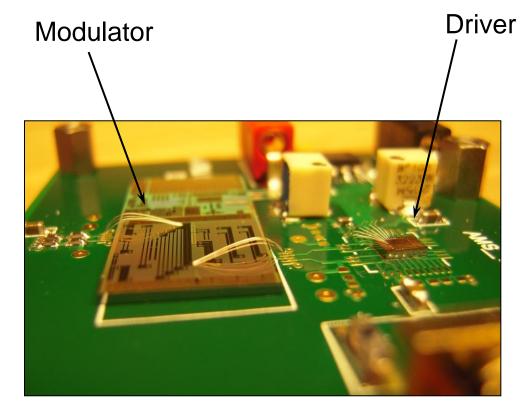

#### 2<sup>nd</sup> Gen driver integrated with modulator based on 0.13um CMOS

### **Achievement in 2013**

#### A complete transceiver link energting at 10Ch/c

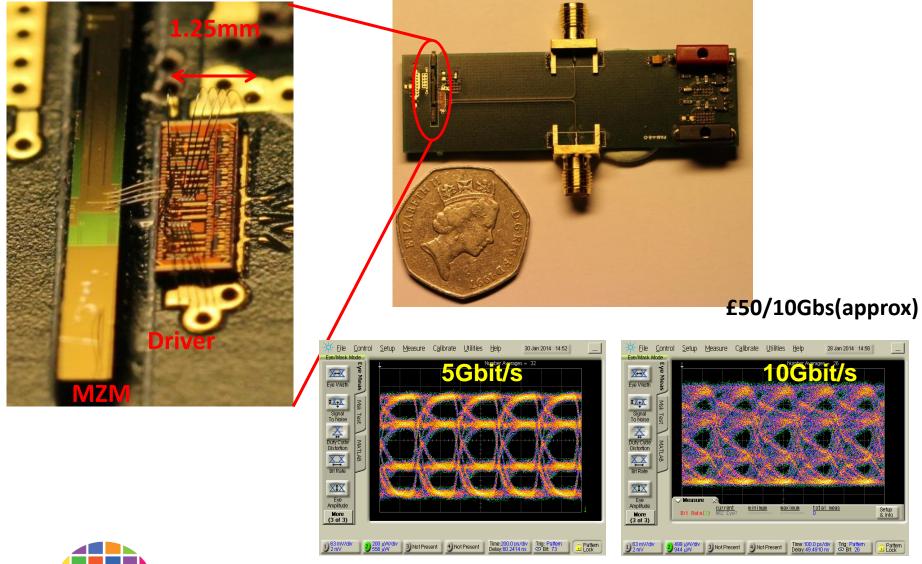

### **Comparison of cost with commercial product**

Intel achieve similar performance at year 2011. Were two years behind Intel. BUT, the cost?

| Product<br>(MZM driver)       | Speed    | Process | Cost of each<br>10Gb/s |

|-------------------------------|----------|---------|------------------------|

| TriQuint TGA-4954             | 10Gb/s   | GaAs    | £119 <sup>1</sup>      |

| Analog Devices<br>ADN2526ACPZ | 11.3Gb/s | SiGe    | £24.19 <sup>1</sup>    |

| SOTON ECS 2013                | 12.5Gb/s | CMOS    | £46.8                  |

Our cost are based on small volume tape out price, and are comparable with commercial products (remarkable!).

Furthermore, we have created a useful research platform!

[1] price obtained from mouser electronic (www.mouser.com)

17

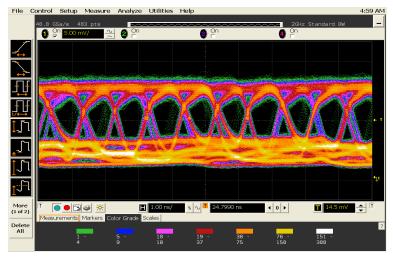

#### **Advanced modulation format realized in 2014**

18

Southampton

#### **Future work**

- Flip Chip Bonding

- Deep sub micron CMOS (65nm and smaller)

- Much faster channels

- Lower Power.

- Better integration with Photonics

- Multiple Channels.

- Coding schemes in hardware and software